基于FPGA的运动控制卡的设计和实现

摘 要:基于FPGA 的运动控制卡采用脉冲加方向的闭环控制方式,具有结构简单,集成度高、实时性好等优点。从硬件的构成、设计和算法实现等方面入手,阐述了运动控制卡的设计和开发。用硬件描述语言VHDL (very high speed integrated circuitHDL)和原理图结合的方式对 FPGA 编程实现系统的主要硬件逻辑和算法,从而提高了系统的灵活性和移植性。在硬件算法上,采用乒乓操作处理高速的分频倍数数据流,提高了系统的实时性和控制精度;并且提出了一种基于加二计数器的分频算法,实现任意分频倍数的分频。利用嵌入式调试工具SignalTap 对运动控制卡进行硬件调试和仿真,给出了相应的误差分析。

关键词:运动控制卡; 伺服电机; 分频; 现场可编程门阵列; 外设部件互连标准总线; 实时; 乒乓操作

Design and realization of motion-controlling-card based on FPGA LI Mu-guo, PENG Ping-liang

0 引言

传统的运动控制卡多采用单片机作为微处理器, 通过一些大规模集成电路实现对伺服电机的控制。由于其结构较为复杂,因此在工作时,存在高频响应慢、控制精度低等缺点。本文提出一种以FPGA (field-programmable gate array) 和PCI9054 接口芯片为核心硬件的运动控制卡,内部硬件接口和算法通过对FPGA 的编程实现。这样,既能很好地克服传统运动控制存在的缺点,又在灵活性和移植性等方面得到了很大的提高。

1 硬件构成与设计

1.1 构成

本文所述的运动控制卡是PCI(peripheral component interconnect)接口卡[1],用Altera 公司生产的型号为 EP1C6Q240C8的FPGA 作为编程逻辑器件,实现所有的硬件算法和反馈信号的检测。采用脉冲加方向[2]的闭环控制方式对电机进行控制。整个运动控制卡系统可用图1 描述。

1.2 设计

运动控制卡硬件电路描述和设计时,严格按照同步时序设计原则[3],而且核心电路用D 触发器实现,电路的主要信号由时钟的上升沿触发器产生。这样可以很好地避免毛刺,并且在布局后仿真和用高速逻辑分析仪采样实际工作信号皆无毛刺。在高速变化的分频倍数数据流控制时,为了保证整个系统的分频输出的实时性,采用如图2 所示的“乒乓操作[3]”技巧。在奇数(2n 1)个缓冲周期时,输入的数据流缓冲到RAMⅠ和从RAMⅡ取出数据到运算模块。在第偶数(2n)个缓冲周期,将数据流缓冲到RAMⅡ,将RAM1 里的数据通过“数据输出选择单元”的选择,送到最后的分频和计数的运算模块进行计算输出。如此循环,周而复始。这种流水线式算法,可以完成数据的无缝缓冲与处理。

本文所述的运动控制卡共涉及总线控制器、分频器、定时器、反馈控制等4 个模块,其原理图如图3 所示。总线控制器完成PCI9054 [4] 局部总线的仲裁逻辑[5]、地址译码和数据流控制,使PCI 数据总线上的数据正确地被译码到各分控制模块进行运算输出。定时器实现硬件定时,计算机通过驱动程序给运动控制卡输入一时间值和一个表示计时开始的控制字,运动控制卡开始计时,在计时完成时,通过产生硬件中断方式 [6],进入中断服务程序,从而实现电机的转角准确定位。我们还可以把一些用户代码作为中断处理子程序,来实现定时切换或运算的功能。分频器实现工作频率(40MHz) 的分频工作,得到控制电机转速的脉冲频率。反馈控制模块实现电机的输出补偿和状态监控功能,可通过读取误差从而实现修正,以此来提高系统控制精度。这些模块在FPGA 内部采用原理图(Schematic Diagrams) VHDL 语言结合的方式进行描述,使逻辑层次更加明确和可读性更强。

本文所述的运动控制卡共涉及总线控制器、分频器、定时器、反馈控制等4 个模块,其原理图如图3 所示。总线控制器完成PCI9054 [4] 局部总线的仲裁逻辑[5]、地址译码和数据流控制,使PCI 数据总线上的数据正确地被译码到各分控制模块进行运算输出。定时器实现硬件定时,计算机通过驱动程序给运动控制卡输入一时间值和一个表示计时开始的控制字,运动控制卡开始计时,在计时完成时,通过产生硬件中断方式 [6],进入中断服务程序,从而实现电机的转角准确定位。我们还可以把一些用户代码作为中断处理子程序,来实现定时切换或运算的功能。分频器实现工作频率(40MHz) 的分频工作,得到控制电机转速的脉冲频率。反馈控制模块实现电机的输出补偿和状态监控功能,可通过读取误差从而实现修正,以此来提高系统控制精度。这些模块在FPGA 内部采用原理图(Schematic Diagrams) VHDL 语言结合的方式进行描述,使逻辑层次更加明确和可读性更强。

2 算法设计

2.1 实时分频算法

运动控制卡输出的不同脉冲频率来实现电机转速的控制,因此脉冲频率的响应速度决定了整个电机的控制精度。这就必然要求我们在设计算法时,要充分考虑分频算法的实时性。本文提出一种基于加二计数器的分频算法,能很好地解决此问题。其算法具体流程图如图4 所示。取锁相输出时钟作为设计的全局时钟,同时用两个单口RAM来交叉刷新分频倍数。加二计数器对输入时钟进行上升沿计数,并对其计数值进行比较判断,如果计数值大于等于两倍的分频倍数,输出为‘1’,否则为‘0’。实现分频器功能。分频器输出即为运动控制卡控制电机转速的脉冲(clk_out)。

2.2 闭环控制算法

整个运动控制卡采用脉冲加方向的控制方式,实现电机的转速和方向的控制。为了保证电机的控制精度,在运动控制卡输出脉冲至电机的驱动器的同时,运动控制卡从编码器中读出反馈脉冲和方向。这样,只要设计两个计数器同时对输出脉冲和反馈脉冲进行计数,并且对两个计数器的计数值进行判断和求差,然后根据求出的差值进行循环插补,即可实现电机的闭环控制。

3 调试和结果仿真

3.1 系统调试

本卡采用Quartus Ⅱ软件自带的SignalTap Ⅱ[7]进行仿真调试,它是一种基于逻辑分析核的嵌入式逻辑分析仪,在使用时,调试人员无需外接专用仪器,就可以通过对FPGA 器件内部所有信号和节点的捕获,来实现对系统故障的分析和判断,整个调试过程非常直观、方便。 SignalTap Ⅱ在采集时钟的上升沿处采集数据,采集时钟的设置不恰当,有时候会得到不能准确反映设计的不期望数据状态,Altera 建议最好使用全局时钟。文中给出以全局时钟gclk 作为采集时钟,1 级触发,并且以RESULT = ELD({HOLD,1})作为触发逻辑[8],其运行分析结果如图5 所示。值得注意的是,在调试完成后,需将SignalTapⅡ文件移除设计目录,以免浪费资源。

3.2 调试结果及误差分析

3.2 调试结果及误差分析

从图5 的调试结果来看,运动控制卡的整个控制服从于总线仲裁逻辑。PCI 和FPGA 数据交换在READY=0 时进行,总线LD 上数据在READY=0 时有效。分频倍数寄存器值改变,分频输出频率即刻作相应改变,满足设计目标。对电机行程(journey1和journey2)、报警(alarm)、零位(zero)和伺服(servo)等外部信号的检测和判断。对反馈回来的时钟进行检测计数。由于PCI 和FPGA 交换数据均发生在系统时钟的上升沿。所以在数据交换过程中,必然会存在一个小于1 个时钟周期的延迟误差。

4 结束语

本文所述的运动控制卡具有如下特点:①数据输入输出口采用光隔离技术[8],来避免一些不必要的干扰;②FPGA采用独立的40MHz 时钟和锁相环设计,保证了系统的时钟稳定;③采用加二分频算法,提高分频输出的实时性;④FPGA 作为核心处理芯片,减少了硬件成本、简化了硬件设计、实时性得到提高;⑤通过状态检测和反馈模块,实现电机的状态检测和误差修正;⑥设计中断定时模块,实现电机的转角控制。

参考文献:

[1] 李贵山,陈金鹏.PCI 局部总线及应用[M].西安:西安电子科技大学出版社,2003:8-16. [2] 周志明. 基于运动控制卡的步进电机控制系统[J]. 煤矿机械,2004(3):95-97. [3] 吴继华,王诚.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005:17-21. [4] PLX Technology Inc. PCI 9054 data book[EB]http://www.plxtech.com/dts/download.aspf=/PCI9000/9054/databook/9054db-21.pdf, 2000. [5] 童鹏,吴新建. PCI9054 芯片接口设计中若干问题的深入研究[J].电子技术应用,2005(10):64-66. [6] 胡刚,石亚伟. PCI总线的中断处理技术[J].计算机自动测量与控制,2001,9(6):55-56. [7] 任爱峰,初秀琴. 基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2005:333-354. [8] 郭佳佳,胡晓菁. 使用SignalTapII逻辑分析仪调试FPGA[J].今日电子,2005(5):45-47.

提交

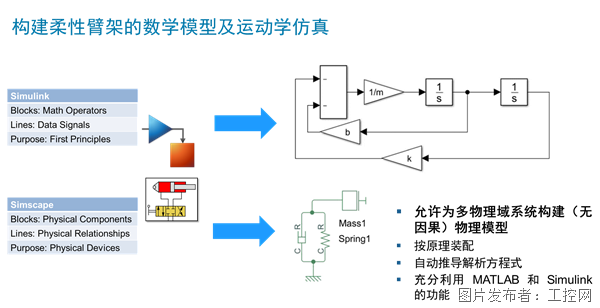

超越传统直觉,MATLAB/Simulink助力重型机械的智能化转型

新大陆自动识别精彩亮相2024华南国际工业博览会

派拓网络被Forrester评为XDR领域领导者

智能工控,存储强基 | 海康威视带来精彩主题演讲

展会|Lubeworks路博流体供料系统精彩亮相AMTS展会

投诉建议

投诉建议